# **CCD** area image sensors

S7033/S7034 series

# **Back-thinned FFT-CCD**

The S7033/S7034 series are families of FFT-CCD image sensors specifically designed for low-light-level detection in scientific applications. The S7033/S7034 series feature large full-well capacity in horizontal CCD register. By using the binning operation, the S7033/S7034 series can be used as a linear image sensor having a long height. This makes the S7033/S7034 series suited for use in spectrophotometry. The binning operation offers significant improvement in S/N and signal processing speed compared with conventional methods by which signals are digitally added by an external circuit.

The S7033/S7034 series have an effective pixel size of  $24 \times 24 \,\mu\text{m}$  and are available in image areas ranging from 12.288 (H)  $\times$  2.928 (V) mm² (S7033-0907, S7034-0907S) up to a large image area of 24.576 (H)  $\times$  2.928 (V) mm² (S7033-1007, S7034-1007S).

Either one-stage or two-stage thermoelectric cooler is built into the package (S7034/S7035 series). At room temperature operation, the device can be cooled down to -10 °C by one-stage cooler and -30 °C by two-stage cooler respectively without using any other cooling technique. In addition since both the CCD chip and the thermoelectric cooler are hermetically sealed, no dry air is required, thus allowing easy handling.

# **Features**

- **■** Line, pixel binning

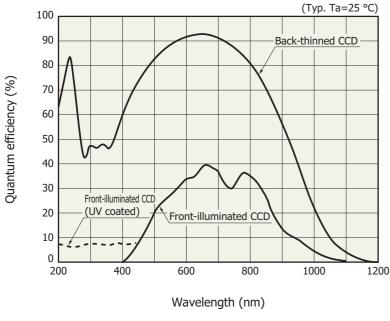

- Greater than 90 % quantum efficiency at peak sensitivity wavelength

- Wide spectral range

- **■** Wide dynamic range

- MPP operation

- **■** Built-in thermoelectric cooler (S7034/S7035 series)

# - Applications

- ➡ Fluorescence spectrometer, ICP

- Industrial inspection requiring

- Semiconductor inspection

- DNA sequencer

- **■** Low-light-level detection

# Selection guide

| Type No.    | Cooling    | Number of total pixels | Number of active pixels | Active area [mm (H) × mm (V)] | Suitable multichannel detector head |

|-------------|------------|------------------------|-------------------------|-------------------------------|-------------------------------------|

| S7033-0907  | Non-cooled | 532 × 128              | 512 × 122               | 12.288 × 2.928                | C7043                               |

| S7033-1007  | Non-cooled | 1044 × 128             | 1024 × 122              | 24.576 × 2.928                | C/043                               |

| S7034-0907S | One-stage  | 532 × 128              | 512 × 122               | 12.288 × 2.928                | C7044                               |

| S7034-1007S | TE-cooled  | 1044 × 128             | 1024 × 122              | 24.576 × 2.928                | C/044                               |

Note: Two-stage TE-cooled type (S7035 series) is also available.

# General ratings

| Parameter              | S7033 series              | S7034 series               |  |  |  |  |

|------------------------|---------------------------|----------------------------|--|--|--|--|

| Pixel size             | 24 (H) × 24 (V) μm        |                            |  |  |  |  |

| Vertical clock phase   | 2 phase                   |                            |  |  |  |  |

| Horizontal clock phase | 2 phase                   |                            |  |  |  |  |

| Output circuit         | One-stage MOSFE           | T source follower          |  |  |  |  |

| Package                | 24 pin ceramic DIP (refer | r to dimensional outlines) |  |  |  |  |

| Built-in cooler        | -                         | One-stage                  |  |  |  |  |

| Window *1              | Quartz glass              | AR-coated sapphire         |  |  |  |  |

<sup>\*1:</sup> Temporary window type (e.g. S7033-0907N) is available upon request.

# **→** Absolute maximum ratings (Ta=25 °C)

| Parameter                | Symbol       | Min. | Тур. | Max. | Unit |

|--------------------------|--------------|------|------|------|------|

| Operating temperature *2 | Topr         | -50  | -    | +50  | °C   |

| Storage temperature      | Tstg         | -50  | -    | +70  | °C   |

| OD voltage               | Vod          | -0.5 | -    | +25  | V    |

| RD voltage               | Vrd          | -0.5 | -    | +18  | V    |

| ISV voltage              | VISV         | -0.5 | -    | +18  | V    |

| ISH voltage              | VISH         | -0.5 | -    | +18  | V    |

| IGV voltage              | VIG1V, VIG2V | -10  | -    | +15  | V    |

| IGH voltage              | VIG1H, VIG2H | -10  | -    | +15  | V    |

| SG voltage               | Vsg          | -10  | -    | +15  | V    |

| OG voltage               | Vog          | -10  | -    | +15  | V    |

| RG voltage               | Vrg          | -10  | -    | +15  | V    |

| TG voltage               | VTG          | -10  | -    | +15  | V    |

| Vertical clock voltage   | VP1V, VP2V   | -10  | -    | +15  | V    |

| Horizontal clock voltage | VP1H, VP2H   | -10  | -    | +15  | V    |

<sup>\*2:</sup> Chip temperature

Note: Exceeding the absolute maximum ratings even momentarily may cause a drop in product quality. Always be sure to use the product within the absolute maximum ratings.

# **□** Operating conditions (MPP mode, Ta=25 °C)

| Parameter                       |                | Symbol       | Min. | Тур. | Max. | Unit       |

|---------------------------------|----------------|--------------|------|------|------|------------|

| Output transistor drain voltage | e              | Vod          | 18   | 20   | 22   | V          |

| Reset drain voltage             |                | VRD          | 11.5 | 12   | 12.5 | V          |

| Output gate voltage             |                | Vog          | 1    | 3    | 5    | V          |

| Substrate voltage               |                | Vss          | -    | 0    | -    | V          |

| Test point (vertical input sour | ce)            | VISV         | -    | VRD  | -    | V          |

| Test point (horizontal input so | ource)         | VISH         | -    | VRD  | -    | V          |

| Test point (vertical input gate | <del>!</del> ) | VIG1V, VIG2V | -9   | -8   | 0    | V          |

| Test point (horizontal input ga | ate)           | VIG1H, VIG2H | -9   | -8   | 0    | V          |

| Vertical shift register         | High           | VP1VH, VP2VH | 4    | 6    | 8    | V          |

| clock voltage                   | Low            | VP1VL, VP2VL | -9   | -8   | -7   | ] <b>v</b> |

| Horizontal shift register       | High           | VP1HH, VP2HH | 4    | 6    | 8    | V          |

| clock voltage                   | Low            | VP1HL, VP2HL | -9   | -8   | -7   | ]          |

| Cumming gate voltage            | High           | Vsgh         | 4    | 6    | 8    | V          |

| Summing gate voltage            | Low            | Vsgl         | -9   | -8   | -7   | \ \ \ \    |

| Donot gate voltage              | High           | VRGH         | 4    | 6    | 8    | V          |

| Reset gate voltage              | Low            | VRGL         | -9   | -8   | -7   | ]          |

| T. 6. 1. 11                     | High           | VTGH         | 4    | 6    | 8    | V          |

| Transfer gate voltage           | Low            | VTGL         | -9   | -8   | -7   | ] <b>v</b> |

| External load resistance        |                | RL           | 20   | 22   | 24   | kΩ         |

# **=** Electrical characteristics (Ta=25 °C)

| Parameter                           |               | Symbol     | Min.    | Тур.    | Max. | Unit |

|-------------------------------------|---------------|------------|---------|---------|------|------|

| Signal output frequency             |               | fc         | -       | 0.25    | 1    | MHz  |

| Vertical shift register capacitance | S703*-0907(S) | CP1V, CP2V | -       | 1500    | -    | nE   |

| vertical shift register capacitance | S703*-1007(S) | CPIV, CPZV | -       | 3000    | -    | pF   |

| Horizontal shift register           | S703*-0907(S) | Ср1н, Ср2н | -       | 260     | -    | nE   |

| capacitance                         | S703*-1007(S) | CPIH, CPZH | -       | 300     | -    | pF   |

| Summing gate capacitance            |               | Csg        | -       | 30      | -    | pF   |

| Reset gate capacitance              |               | Crg        | -       | 30      | -    | pF   |

| Transfer gate canacitance           | S703*-0907(S) | Стд        | -       | 60      | -    | nE   |

| Transfer gate capacitance           | S703*-1007(S) | CIG        | -       | 80      | -    | pF   |

| Charge transfer efficiency *3       |               | Сте        | 0.99995 | 0.99999 | -    | -    |

| DC output level *4                  |               | Vout       | 12      | 15      | 18   | V    |

| Output impedance *4                 |               | Zo         | -       | 2       | 3    | kΩ   |

| Power consumption *4 *5             |               | Р          | -       | 13      | 14   | mW   |

<sup>\*3:</sup> Charge transfer efficiency per pixel, measured at half of the full well capacity

<sup>\*5:</sup> Power consumption of the on-chip amplifier plus load resistance

<sup>\*4:</sup> The values depend on the load resistance. (Typ. Vop=20 V, Load resistance=22  $k\Omega$ )

# **■** Electrical and optical characteristics (Ta=25 °C, unless otherwise noted)

| Parameter       |                           | Symbol          | Min. | Тур.  | Max.        | Unit |            |  |

|-----------------|---------------------------|-----------------|------|-------|-------------|------|------------|--|

| Saturation out  | Saturation output voltage |                 | Vsat | -     | Fw × Sv     | -    | V          |  |

| Full well capa  | oit .                     | Vertical        | Fw   | 240   | 320         | -    | ke-        |  |

| Full well capac | Lity                      | Horizontal *6   | ΓW   | 2700  | 3400        | -    | , ke       |  |

| CCD node sen    | sitivity                  |                 | Sv   | 0.5   | 0.6         | -    | μV/e⁻      |  |

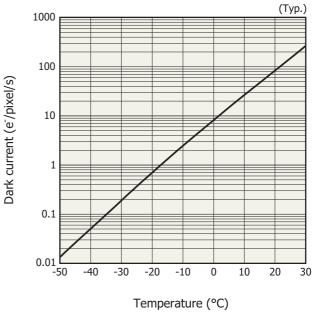

| Dark current *  | 7                         | 25 °C           | DC   | -     | 100         | 1000 | o-/nivol/c |  |

| (MPP mode)      |                           | 0 °C            | - DS | -     | 10          | 100  | e-/pixel/s |  |

| Readout noise   | *8                        |                 | Nr   | -     | 30          | 45   | e- rms     |  |

| Dynamic rang    | o *9                      | Line binning    | DR   | 90000 | 113300      | -    | _          |  |

| Dynamic rang    | E '                       | Area scanning   | DK   | 8000  | 10700       | -    |            |  |

| Photo respons   | se non-uniformity *10     | )               | PRNU | -     | ±3          | ±10  | %          |  |

| Spectral respo  | nse range                 |                 | λ    | -     | 200 to 1100 | -    | nm         |  |

|                 | Point defect *11          |                 |      | -     | -           | 0    |            |  |

| Blemish         | Politi delect             | Black spot      | _    | -     | -           | 10   | ]          |  |

| DICITIISH       | Cluster defect *12        | ster defect *12 |      | -     | -           | 3    | ] -        |  |

|                 | column defect *13         |                 |      | -     | -           | 0    |            |  |

<sup>\*6:</sup> The linearity is ±1.5 %.

Photo response non-uniformity (PRNU) =

$$\frac{\text{Fixed pattern noise (peak to peak)}}{\text{Signal}} \times 100 \, [\%]$$

\*11: White spots

Pixels whose dark current is higher than 1 ke $^{\!\scriptscriptstyle -}$  after one-second integration at 0 °C.

Black spots

Pixels whose sensitivity is lower than one-half of the average pixel output. (Measured with uniform light producing one-half of the saturation charge)

- \*12: 2 to 9 contiguous defective pixels

- \*13: 10 or more contiguous defective pixels

# Spectral response (without window) \*14

KMPDB0058EB

\*14: Spectral response with quartz glass or sapphire are decreased by the transmittance.

<sup>\*7:</sup> Dark current nearly doubles for every 5 to 7 °C increase in temperature.

<sup>\*8:</sup> Operating frequency is 150 kHz.

<sup>\*9:</sup> Dynamic range (DR)=Full well/Readout noise

<sup>\*10:</sup> Measured at the half of the full well capacity output.

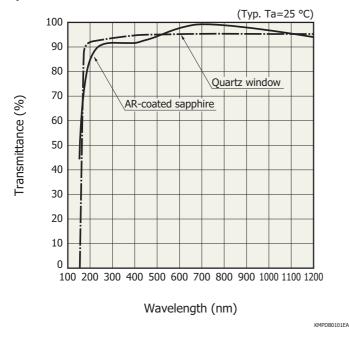

# Spectral transmittance characteristics of window material

# **➡** Window material

| Type No.                   | Window material        |

|----------------------------|------------------------|

| S7033 series               | Quartz glass *15       |

| 37033 Series               | (option: window-less)  |

| S7034 series               | AR-coated sapphire *16 |

| 37034 Series               | (option: window-less)  |

| S7035 series               | AR-coated sapphire *16 |

| (two-stage TE-cooled type) | (option: window-less)  |

# **Dark current vs. temperature**

KMPDB0256EA

<sup>\*15:</sup> Resin sealing \*16: Hermetic sealing

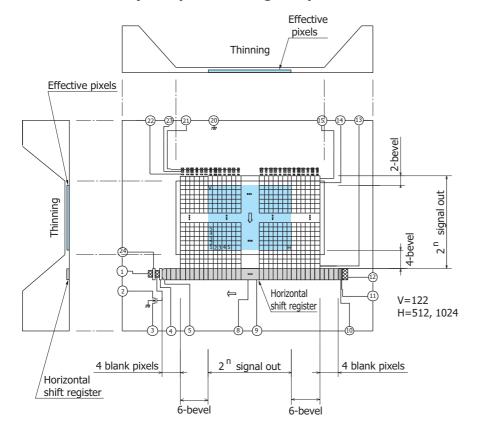

# Device structure (conceptual drawing of top view in dimensional outlines)

Note: When viewed from the direction of the incident light, the horizontal shift register is covered with a thick silicon layer (dead layer). However, long-wavelength light passes through the silicon dead layer and may possibly be detected by the horizontal shift register. To prevent this, provide light shield on that area as needed.

KMPDC0076EB

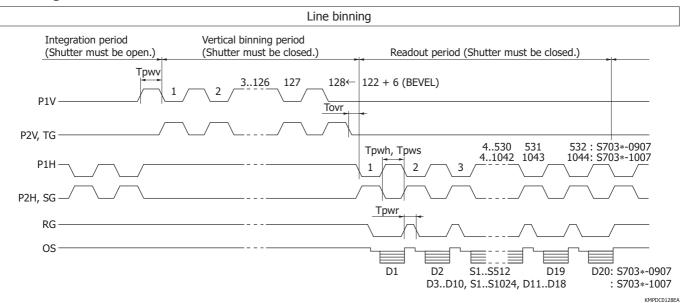

# Timing chart

| Р                            | arameter           | Symbol     | Min.  | Тур. | Max. | Unit |

|------------------------------|--------------------|------------|-------|------|------|------|

| P1V, P2V, TG * <sup>17</sup> | Pulse width        | Tpwv       | 6 *18 | 8    | -    | μs   |

| PIV, PZV, IG **              | Rise and fall time | Tprv, Tpfv | 10    | -    | -    | ns   |

|                              | Pulse width        | Tpwh       | 500   | 2000 | -    | ns   |

| P1H, P2H *17                 | Rise and fall time | Tprh, Tpfh | 10    | -    | -    | ns   |

|                              | Duty ratio         | -          | -     | 50   | -    | %    |

|                              | Pulse width        | Tpws       | 500   | 2000 | -    | ns   |

| SG                           | Rise and fall time | Tprs, Tpfs | 10    | -    | -    | ns   |

|                              | Duty ratio         | -          | -     | 50   | -    | %    |

| RG                           | Pulse width        | Tpwr       | 100   | -    | -    | ns   |

| KG                           | Rise and fall time | Tprr, Tpfr | 5     | -    | -    | ns   |

| TG-P1H                       | Overlap time       | Tovr       | 3     | -    | -    | μs   |

$<sup>^{*}17:</sup>$  Symmetrical clock pulses should be overlapped at 50 % of maximum amplitude.  $^{*}18:$  In case of the S7033-1007, S7034-1007S

### Area scanning (large full well mode) Integration period (Shutter must be open.) Readout period (Shutter must be closed.) Tpwy 4..127 128←122 + 6 (Bevel) P1V P2V, TG P1H ||||||||| P2H, SG [[[]]] RG OS-Enlarged view Tovr Tpwh, Tpws P2V, TG P1H P2H, SG Tpwr RG OS S1..S512 D2 D3 D18 D19 D20: S703\*-0907 D5..D10, S1..S1024, D11..D17 : S703\*-1007

| Parameter        |                    | Symbol     | Min.  | Тур. | Max. | Unit |

|------------------|--------------------|------------|-------|------|------|------|

| P1V, P2V, TG *19 | Pulse width        | Tpwv       | 6 *20 | 8    | -    | μs   |

| P1V, P2V, 1G 19  | Rise and fall time | Tprv, Tpfv | 10    | -    | -    | ns   |

|                  | Pulse width        | Tpwh       | 500   | 2000 | -    | ns   |

| P1H, P2H *19     | Rise and fall time | Tprh, Tpfh | 10    | -    | -    | ns   |

|                  | Duty ratio         | -          | -     | 50   | -    | %    |

|                  | Pulse width        | Tpws       | 500   | 2000 | -    | ns   |

| SG               | Rise and fall time | Tprs, Tpfs | 10    | -    | -    | ns   |

|                  | Duty ratio         | -          | -     | 50   | -    | %    |

| RG               | Pulse width        | Tpwr       | 100   | -    | -    | ns   |

| KG               | Rise and fall time | Tprr, Tpfr | 5     | -    | -    | ns   |

| TG-P1H           | Overlap time       | Tovr       | 3     | -    | _    | US   |

<sup>\*19:</sup> Symmetrical pulses should be overlapped at 50 % of maximum amplitude.

<sup>\*20:</sup> In case of the 7033-1007, S7034-1007S

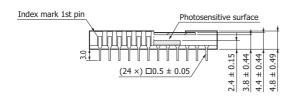

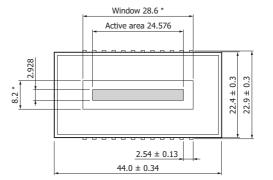

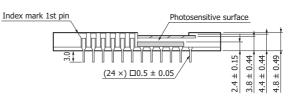

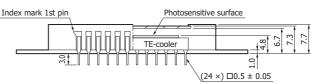

# Dimensional outlines (unit: mm)

# \$7033-0907 Window 16.3 \* Active area 12.288 12.288 2.54 ± 0.13

$34.0 \pm 0.34$

\* Size of window that guarantees the transmittance in the "Spectral transmittance characteristics" graph

KMPDA0080EC

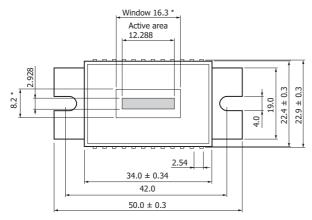

# S7033-1007

\* Size of window that guarantees the transmittance in the "Spectral transmittance characteristics" graph

KMPDA0081EC

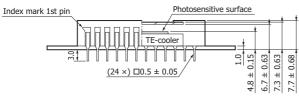

# S7034-0907S

\* Size of window that guarantees the transmittance in the "Spectral transmittance characteristics" graph

KMPDA0082ED

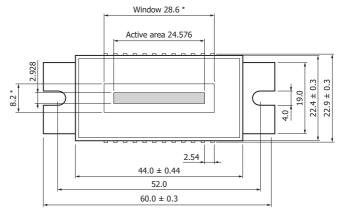

# S7034-1007S

\* Size of window that guarantees the transmittance in the "Spectral transmittance characteristics" graph

KMPDA0083ED

# **₽** Pin connections

| Pin | S7033 series |                                      |        | S7034 series                         | Remark               |

|-----|--------------|--------------------------------------|--------|--------------------------------------|----------------------|

| No. | Symbol       | Function                             | Symbol | Function                             | (standard operation) |

| 1   | RD           | Reset drain                          | RD     | Reset drain                          | +12 V                |

| 2   | OS           | Output transistor source             | OS     | Output transistor source             | RL=22 kΩ             |

| 3   | OD           | Output transistor drain              | OD     | Output transistor drain              | +20 V                |

| 4   | OG           | Output gate                          | OG     | Output gate                          | +3 V                 |

| 5   | SG           | Summing gate                         | SG     | Summing gate                         | Same pulse as P2H    |

| 6   | -            |                                      | -      |                                      |                      |

| 7   | -            |                                      | -      |                                      |                      |

| 8   | P2H          | CCD horizontal register clock-2      | P2H    | CCD horizontal register clock-2      |                      |

| 9   | P1H          | CCD horizontal register clock-1      | P1H    | CCD horizontal register clock-1      |                      |

| 10  | IG2H         | Test point (horizontal input gate-2) | IG2H   | Test point (horizontal input gate-2) | -8 V                 |

| 11  | IG1H         | Test point (horizontal input gate-1) | IG1H   | Test point (horizontal input gate-1) | -8 V                 |

| 12  | ISH          | Test point (horizontal input source) | ISH    | Test point (horizontal input source) | Connect to RD        |

| 13  | TG *21       | Transfer gate                        | TG *21 | Transfer gate                        | Same pulse as P2V    |

| 14  | P2V          | CCD vertical register clock-2        | P2V    | CCD vertical register clock-2        |                      |

| 15  | P1V          | CCD vertical register clock-1        | P1V    | CCD vertical register clock-1        |                      |

| 16  | -            |                                      | Th1    | Thermistor                           |                      |

| 17  | -            |                                      | Th2    | Thermistor                           |                      |

| 18  | -            |                                      | P-     | TE-cooler-                           |                      |

| 19  | -            |                                      | P+     | TE-cooler+                           |                      |

| 20  | SS           | Substrate (GND)                      | SS     | Substrate (GND)                      | GND                  |

| 21  | ISV          | Test point (vertical input source)   | ISV    | Test point (vertical input source)   | Connect to RD        |

| 22  | IG2V         | Test point (vertical input gate-2)   | IG2V   | Test point (vertical input gate-2)   | -8 V                 |

| 23  | IG1V         | Test point (vertical input gate-1)   | IG1V   | Test point (vertical input gate-1)   | -8 V                 |

| 24  | RG           | Reset gate                           | RG     | Reset gate                           |                      |

<sup>\*21:</sup> Isolation gate between vertical register and horizontal register.

In standard operation, TG should be applied the same pulse as P2V.

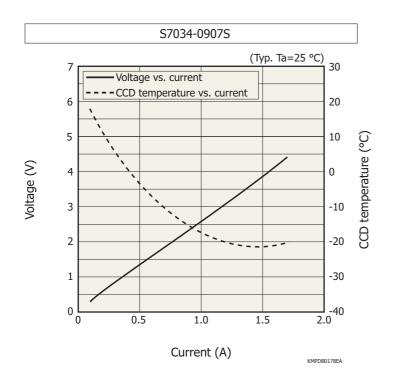

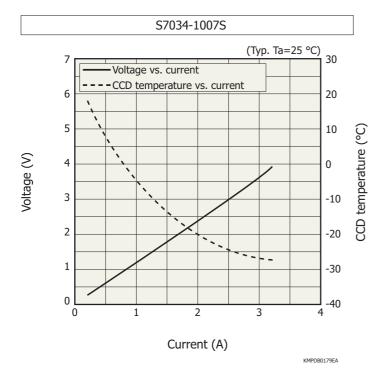

# **Specifications of built-in TE-cooler (Typ.)**

| Parameter                                  | Symbol | Condition           | S7034-0907S | S7034-1007S | Unit |

|--------------------------------------------|--------|---------------------|-------------|-------------|------|

| Internal resistance                        | Rint   | Ta=25 °C            | 2.5         | 1.2         | Ω    |

| Maximum current *22                        | Imax   | Tc *23=Th *24=25 °C | 1.5         | 3.0         | Α    |

| Maximum voltage                            | Vmax   | Tc *23=Th *24=25 °C | 3.8         | 3.6         | V    |

| Maximum heat absorption *25                | Qmax   |                     | 3.4         | 5.1         | W    |

| Maximum temperature of heat radiating side | -      |                     | 70          | 70          | °C   |

<sup>\*22:</sup> If the current greater than this value flows into the thermoelectric cooler, the heat absorption begins to decrease due to the Joule heat. It should be noted that this value is not the damage threshold value. To protect the thermoelectric cooler and maintain stable operation, the supply current should be less than 60 % of this maximum current.

<sup>\*23:</sup> Temperature of the cooling side of thermoelectric cooler

<sup>\*24:</sup> Temperature of the heat radiating side of thermoelectric cooler

<sup>\*25:</sup> This is a theoretical heat absorption level that offsets the temperature difference in the thermoelectric cooler when the maximum current is supplied to the unit.

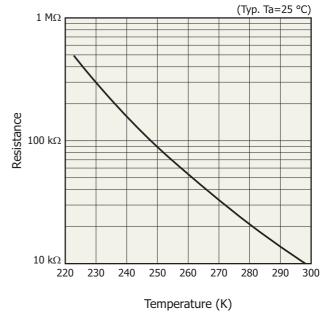

# Specifications of built-in temperature sensor

A chip thermistor is built in the same package with a CCD chip, and the CCD chip temperature can be monitored with it. A relation between the thermistor resistance and absolute temperature is expressed by the following equation.

$R_{T1} = R_{T2} \times exp B_{T1/T2} (1/T1 - 1/T2)$

R<sub>T1</sub>: resistance at absolute temperature T1 [K] R<sub>T2</sub>: resistance at absolute temperature T2 [K]

BT1/T2: B constant [K]

The characteristics of the thermistor used are as follows.

$R_{298}=10 \text{ k}\Omega$   $B_{298/323}=3450 \text{ K}$

KMPDB0111EA

# Precaution for use (electrostatic countermeasures)

- Handle these sensors with bare hands or wearing cotton gloves. In addition, wear anti-static clothing or use a wrist band with an earth ring, in order to prevent electrostatic damage due to electrical charges from friction.

- Avoid directly placing these sensors on a work-desk or work-bench that may carry an electrostatic charge.

- Provide ground lines or ground connection with the work-floor, work-desk and work-bench to allow static electricity to discharge.

- Ground the tools used to handle these sensors, such as tweezers and soldering irons.

It is not always necessary to provide all the electrostatic measures stated above. Implement these measures according to the amount of damage that occurs.

# Element cooling/heating temperature incline rate

Element cooling/heating temperature incline rate should be set at less than 5 K/min.

# Multichannel detector head C7043, C7044

### Features

C7043: for S7033 series C7044: for S7034 series

■ Area scanning or full line-binnng operation

→ Readout frequency: 250 kHz

→ Readout noise: 60 e<sup>-</sup> rms

Arr  $\Delta$ T=50 °C ( $\Delta$ T changes by cooling method.)

| Input          | Symbol          | Value                            |

|----------------|-----------------|----------------------------------|

|                | V <sub>D1</sub> | +5 Vdc, 200 mA                   |

|                | VA1+            | +15 Vdc, +100 mA                 |

|                | VA1-            | -15 Vdc, -100 mA                 |

| Supply voltage | VA2             | +24 Vdc, 30 mA                   |

|                | V <sub>D2</sub> | +5 Vdc, 30 mA (C7044)            |

|                | Vp              | +5 Vdc, 2.5 A (C7044)            |

|                | VF              | +12 Vdc, 100 mA (C7044)          |

| Master start   | φms             | HCMOS logic compatible           |

| Master clock   | фтс             | HCMOS logic compatible,<br>1 MHz |

Information described in this material is current as of February, 2014.

Product specifications are subject to change without prior notice due to improvements or other reasons. This document has been carefully prepared and the information contained is believed to be accurate. In rare cases, however, there may be inaccuracies such as text errors. Before using these products, always contact us for the delivery specification sheet to check the latest specifications.

Type numbers of products listed in the delivery specification sheets or supplied as samples may have a suffix "(X)" which means preliminary specifications or a suffix "(Z)" which means developmental specifications.

The product warranty is valid for one year after delivery and is limited to product repair or replacement for defects discovered and reported to us within that one year period. However, even if within the warranty period we accept absolutely no liability for any loss caused by natural disasters or improper product use.

Copying or reprinting the contents described in this material in whole or in part is prohibited without our prior permission.

# **HAMAMATSU**

www.hamamatsu.com

HAMAMATSU PHOTONICS K.K., Solid State Division

1126-1 Ichino-cho, Higashi-ku, Hamamatsu City, 435-8558 Japan, Telephone: (81) 53-434-3311, Fax: (81) 53-434-5184

U.S.A.: Hamamatsu Corporation: 360 Foothill Road, P.O.Box 6910, Bridgewater, N.J. 08807-0910, U.S.A., Telephone: (1) 908-231-0960, Fax: (1) 908-231-1218

Germany: Hamamatsu Photonics Deutschland GmbH: Arzbergerstr. 10, D-82211 Herrsching am Ammersee, Germany, Telephone: (49) 8152-375-0, Fax: (49) 8152-265-8

France: Hamamatsu Photonics France S.A.R.L.: 19, Rue du Saule Trapu, Parc du Moulin de Massy, 91882 Massy Cedex, France, Telephone: 33-(1) 69 53 71 00, Fax: 33-(1) 69 53 71 00

United Kingdom: Hamamatsu Photonics UK Limited: 2 Howard Court, 10 Tewin Road, Welwyn Garden City, Hertfordshire AL7 1BW, United Kingdom, Telephone: (44) 1707-294888, Fax: (44) 1707-325777

North Europe: Hamamatsu Photonics Norden AB: Thorshamnsgatan 35 16440 Kista, Sweden, Telephone: (46) 8-509-031-00, Fax: (46) 8-509-031-01

Italy: Hamamatsu Photonics Italia S.R.L.: Strada della Moia, 1 int. 6, 20020 Arese, (Milano), Italy, Telephone: (39) 02-935-81-733, Fax: (39) 02-935-81-741

China: Hamamatsu Photonics (China) Co., Ltd.: 1201 Tower B, Jiaming Center, No.27 Dongsanhuan Beilu, Chaoyang District, Beijing 100020, China, Telephone: (86) 10-6586-6006, Fax: (86) 10-6586-2866